AlGaN/GaN HEMTs have successfully demonstrated promising potential in high frequency and power electronics applications. However, for a high voltage AlGaN/GaN HEMT working at switching mode, the current collapse effect always results in dynamic performance degradation. Field-plates have demonstrated their effectivenesses on dynamic performances improvement in AlGaN/GaN HEMTs.

A novel double-gate AlGaN/GaN HEMT has been proposed by Suzhou Institute of Nano-Tech & Nano-Bionics,CAS (SINANO) to study the dynamic performance of the devices with SFP and GFP.The new findings in the mechanisms of the SFP and GFP were published on IEEE Electron Device Letters(vol.34, p.217, 2013).The famous international Semiconductor magazine---Semiconductor Today reported the findings(Original link).

Recently, a novel switching mode was demonstrated by SINANO to improve the dynamic performances of the DG-AlGaN/GaN HEMT, which is:During the device’s on-state, the top-gate voltage (VTG_on_state) is set at positive voltage; During the device’s off-state, the top-gate voltage (VTG_off_state) is biased at 0V. Based on this driving mode, the dynamic performances can be much improved. This driving mode also allows researchers to analyzed the dynamic resistances in drift region.The results indicate that the current collapse at drain side gate edge more affects the τfd, while the “current collapse” in the drift region close to the drain more affects the Ron_D. It was published on IEEE Electron Device Letters (vol.34, p.747, 2013). Semiconductor Today reported these research results(Original link).

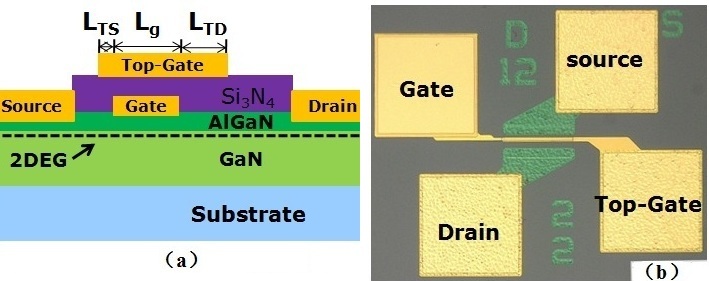

Fig. 1 (a) Schematic cross-sectional diagram of a double-gate AlGaN/GaN HEMT (DG-HEMT),

(b) The optical image of the DG-HEMT.(Image by SINNAO)

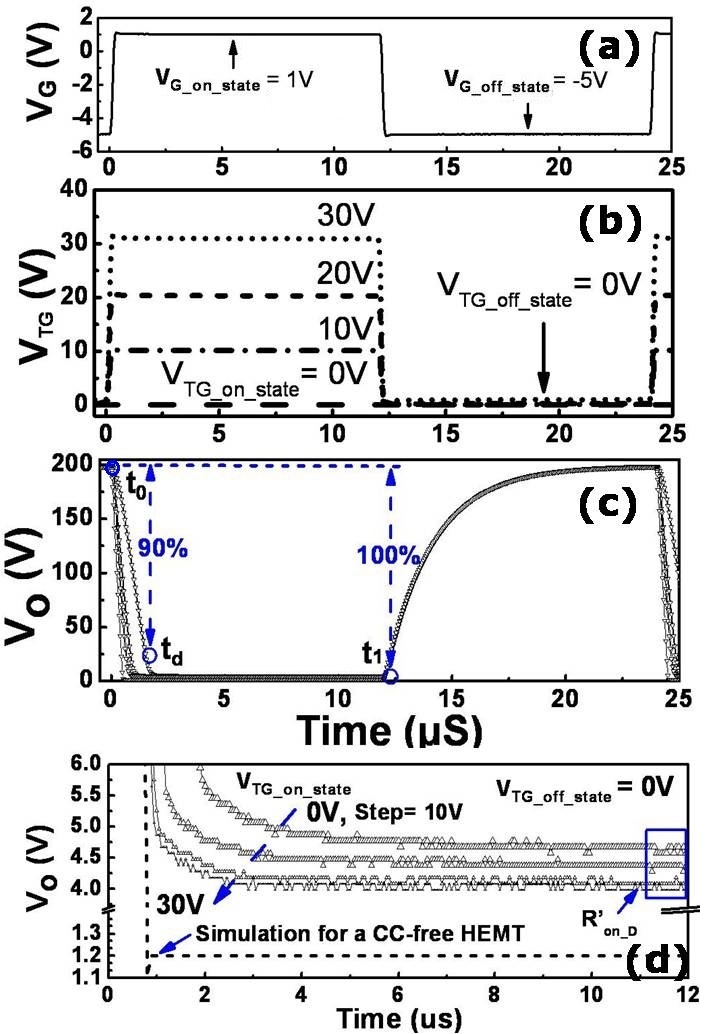

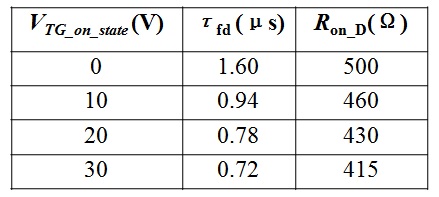

The on-state top-gate voltage (VTG_on_state) is biased from 0V to 30V. The off-state top-gate voltage (VTG_off_state) is constantly biased at 0V. The dynamic characteristic is becoming better as the increasing of the top-gate’s voltage as show in Fig. 2. Table 1 lists the impacts of VTG_on_state on the τfd and the Ron_D. When VTG_on_state is set at 0V that corresponds to SFP mode, the τfd and the Ron_D are 1.6μs and 500Ω, respectively. When VTG_on_state increases to 30V, the τfd and the Ron_D decrease to 0.72μs and 415Ω, improved by 55% and 17%, respectively.

Fig. 2. (a) (b) (c) Input pulse signals and drain output voltage (Vo) waveforms of a DG-HEMT.

(d) Drain output voltage (Vo) waveforms of a DG-HEMT working at the on-state pulse mode(Image by SINANO).

Table. 1 τfd and Ron_D vs. On-state top-gate voltage

downloadFile